## Open Source Hardware and EDA Tools for Analog/Mixed-Signal Design and Prototyping

Naohiko Shimizu, Junichi Akita, Marie-Minerve Louërat, Haralampos-G. Stratigopoulos, Jean-Paul Chaput, Dimitri Galayko

#### ▶ To cite this version:

Naohiko Shimizu, Junichi Akita, Marie-Minerve Louërat, Haralampos-G. Stratigopoulos, Jean-Paul Chaput, et al.. Open Source Hardware and EDA Tools for Analog/Mixed-Signal Design and Prototyping. 2018 IEEE International Symposium on Circuits and Systems (ISCAS), May 2018, Florence, Italy. 10.1109/ISCAS.2018.8351884. hal-01843031

### HAL Id: hal-01843031

https://hal.sorbonne-universite.fr/hal-01843031v1

Submitted on 18 Jul 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Open Source Hardware and EDA Tools for Analog/Mixed-Signal Design and Prototyping

Naohiko Shimizu Department of Embedded Technology Tokai University Tokyo, Japan

Email: nshimizu@keyaki.cc.u-tokai.ac.jp

Junichi Akita

Interface Device Laboratory

Institute of Science and Engineering

Faculty of Electrical and Computer Engineering

Kanazawa University

Kanazawa, Japan

Email: akita@is.t.kanazawa-u.ac.jp

Marie-Minerve Louërat,

Haralampos-G. Stratigopoulos,

Jean-Paul Chaput,

and Dimitri Galayko

Sorbonne Université, CNRS, LIP6

Paris, France

Email: firstName.lastName@lip6.fr

Abstract—The paper aims at stimulating a discussion on the prospect and potentiality of open source electronic design automation tools and open source hardware. We discuss the benefits and motivation, as well as the expected difficulties and shortcomings. Finally, we provide a representative list of efforts as of today specifically for analog and mixed-signal circuits and systems design and prototyping.

#### I. INTRODUCTION

Electronic Design Automation (EDA) tools aiming to perform modeling, design, simulation, verification, design-fortest, etc., of electronic circuits and systems are commercialized and, thereby, "un-democratized", in the sense that licenses come at a price that is prohibitive for individuals and in many cases for Universities and small and medium size enterprises as well. Even if access to EDA tools is granted, the subsequent circuit fabrication and hardware prototyping steps are also very costly and cannot be easily afforded either.

In light of this reality, as of today there have been many attempts towards open source EDA tools (OSEDA) and open source hardware (OSHW), turning electronic circuits and systems design from being a "privilege" to being accessible at a personal scale [1]. Open source in this context means that the source code of EDA tools and netlist, layout, benchmark suites, etc., of a hardware design, are made publicly available and are freely distributed with no discrimination against persons or groups, and, thereby, they can not only be used freely, but can also be modified and enhanced with new features for the specific needs of a project [2]. Furthermore, a first version of OSEDA or OSHW can continuously evolve through the work of additional, multiple, and independent contributors in a collaborative spirit.

OSEDA can be considered as part of the free open software movement [3] and OSHW can be considered as part of the worldwide makers movement or a technology-based extension of the Do-It-Yourself (DIY) movement [4], [5].

One of the first pioneers of OSEDA was University of California, Berkeley, proposing a variety of tools for circuit design [7]. Perhaps the most popular OSHW nowadays is Arduino [8], which offers the possibility of fast hardware

prototyping without requiring the user to have a strong background in electronics and programming. Historically, OSEDA and OSHW have been developed more intensively for digital circuits compared to their analog counterparts [5]. For example, Alliance [9], [10], which is a tool for digital integrated circuit design allowing the automated synthesis of a circuit from Registered Transfer Level (RTL) description to Graphic Database System (GDSII) description, was proposed in the early 90s. An excellent and comprehensive review of OSEDA and OSHW efforts, as well as existing project repositories (for example, see [11]–[13]), can be found in [14]. The ongoing project "Open!" is studying the current practices in open source project development [6].

In this paper, we provide some representative examples of existing and under development OSEDA and OSHW specifically for analog and mixed-signal (AMS) circuit design and prototyping. Due to space limitations the list is not meant to be complete. Section II discusses the benefits from widely adopting OSEDA and OSHW which explains the growing interest of the designers community. Section III discusses the difficulties for OSEDA and OSHW to become a reality and common practice. Section IV provides the examples and Section V concludes the paper.

#### II. MOTIVATION FOR OSHW AND OSEDA

OSHW and OSEDA will greatly increase the number of individuals (i.e. makers, passionates of electronics, curious, etc.) who can perform designs. It will also allow small and medium size enterprises that do not necessarily have the capital to purchase licenses of proprietary tools and hardware platforms to perform designs. The larger pool of designers created by OSHW and OSEDA implies that innovation will be brought up at a faster pace. There will be more innovation and higher productivity through reuse especially on what it concerns application-specific integrated circuits, thus allowing the development of new products and applications. As a result, OSHW and OSEDA can facilitate the proliferation of electronic circuits, extending their deployment in a broader range of applications.

OSHW and OSEDA will be valuable for supporting teaching activities on electronics at Universities even in countries and continents that have limited financial means. Students anywhere in the world will be able to put their hands on actual designs, learn, experiment, and even make silicon demonstrators. OSHW and OSEDA can be used even in secondary education such that students get exposure to electronic design and design automation at a very early stage.

OSEDA will bring down drastically the cost of designing an integrated circuit. This not only reduces the final product cost, but also allows the design companies to invest the amount that would be spent otherwise to purchase licenses of proprietary tools for other purposes, such as performing more design iterations, fabricating more prototypes, and adding more features into the design that often are overlooked due to cost factors, i.e. built-in test infrastructure, security, reliability, self-repair, fault tolerance, etc.

Since the number of designers increases and the cost of design drops, there will be more designs that reach a silicon implementation, thus overall there will be more clients for the foundries. Apart from the economic benefit, this will sustain a high volume manufacturing of devices in a current technology for a longer period. Therefore, the investment on a foundry, which is typically in the order of tens of billions of U.S. dollars, will amortize itself faster and, in general, the phenomenon of rapid technology obsolesce will slow down. In addition, we may observe the sustainability of foundries in several countries, thus partially alleviating security and trust concerns, such as IC/IP piracy, counterfeiting, overproduction, etc., that are due to outsourcing and the globalization of the manufacturing chain of electronic components.

OSEDA may motivate or even force in the end foundries to freely distribute their process design kits (PDK). This will circumvent complications that designers often experience with the signing of the Non Disclosure Agreement (NDA). For example, often in the case of academic projects the foundry demands the ownership of the design.

OSHW and OSEDA will also facilitate the creation of benchmark circuits that can be used for demonstrating and comparing concepts. It is often the case that for a given problem numerous solutions are proposed in the literature, but it is impossible to perform a quantitative comparison because the underlying case studies in each paper, i.e. circuit, topology, technology, etc., are different. Benchmarks can help evaluating and comparing solutions on common grounds, thus offering more credibility to published papers and avoiding the flood of literature. Benchmarks can help also practitioners selecting much faster the best solution for a given application.

EDA companies tend to decompose the tool for performing and completing successfully a design into several individual tools, each requiring a different license. OSEDA could target an all-in-one tool or combine OSEDA tools with licensed tools.

Using proprietary tools for which the source code is not available introduces various trustworthiness and security threats. In particular, there are various vulnerable points that can be exploited by a knowledgeable adversary to introduce Hardware Trojans. Hardware Trojans are malicious modifications in an IC aiming at covertly leaking secret information, such as cipher keys in a cryptoprocessor, degrading the reliability and performance, rendering the IC completely malfunctional, or bringing the IC at a denial of service state. OSEDA can offer full transparency for the user who, in turn, will have full control over the design. Assuming a chip designed entirely with OSEDA and a trusted foundry, the Hardware Trojans threat is eradicated.

It is commonly accepted that the benefits from OSHW would be greater if it is supported by publicly available documentation regarding the EDA tools that were employed to develop the OSHW [15]. OSEDA is a key factor to reach this goal.

OSHW and OSEDA are based on the principle that anyone can be a user of a released version and a contributor in a future version. The different versions can also be traced back to understand the evolution. In this regards, OSHW and OSEDA become automatically world heritage that is by default preserved indefinitely and can further evolve at any chosen time even after a long period of silence [16].

## III. DIFFICULTIES AND CHALLENGES FOR OSHW & OSEDA TO BECOME REALITY

If a large number of chip designers start relying on OSEDA, then EDA companies will face financial losses and this may bring them out of business resulting in significant job cuts. A new business model will be needed, perhaps a support-oriented business model. Nevertheless, as explained above, OSEDA are expected also to create jobs and even new markets, thus the job cuts in the EDA industry may be counterbalanced.

Continuous and quick maintenance and debugging of OSEDA is not guaranteed. Typically, a group of core developers makes public a first version of the tool and stays active for some time processing demands for fixing bugs in reasonable time. However, core developers may at some point withdraw, retire, loose interest, etc., thus the maintenance and debugging risk to be slowed down or totally discontinued. Users then may loose interest in the tool if bugs cannot be fixed or new features cannot be added, and the tool may eventually become obsolete.

OSHW and OSEDA must be extensively validated and verified before usage. The presence of errors and bugs may result in erroneous, lower-performance, and non-manufacturable designs. Ideally, many potential users should play the role of testers to validate and verify the beta versions. However, this is not guaranteed, thus reducing the confidence of the end users and affecting the spreading and popularity of OSHW and OSEDA.

It is unclear if foundries will accept to openly share their PDKs in the context of OSEDA. This is especially true for advanced technology nodes where confidentiality rises. Thus, OSHW and OSEDA in the end may be only linked to old and obsolete technology nodes without offering the possibility of performing state-of-the-art designs.

Academia is typically behind the development OSHW and OSEDA, but securing sufficient funding to develop OSHW and OSEDA is not straightforward. It is unclear which bodies (i.e. universities, governments, donors, etc.) will accept to provide generous funding to boost the development of OSHW and OSEDA and whether this funding will be uninterrupted.

Many developers despite being in favor of OSEDA and actually having this goal at the initial stages of the development, in the end they choose rather to pursue a technology transfer or the creation of a start-up since the economic incentive becomes too high. In general, the success of OSHW and OSEDA will largely depend on devoted and knowledgeable volunteers and passionates and on the rise of a spirit of open source consciousness in the design and EDA communities.

## IV. EXAMPLES OF OSEDA AND OSHW FOR AMS CIRCUIT DESIGN AND PROTOTYPING

#### A. MakeLSI: Project

MakeLSI: Project is a project aiming at realizing an open source Large Scale Integration (LSI) design and fabrication community [17]. The project started using the FAIS Semiconductor Center [18], which is a commonly operated LSI fabrication facility in Kitakyushu, Japan. FAIS offers a  $2\mu m$ , two-metal layer CMOS technology, with a simple and clear lambda-based design rule. Using the PDK does not require signing a NDA and, in addition, the users are free to share and distribute their circuit designs. Finally, the cost to fabricate a wafer is affordable and suitable for training and educational purposes and even for hobbyists.

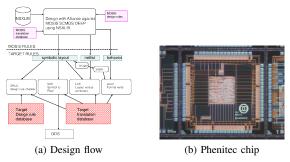

Fig. 1. OSEDA tools used in "MakeLSI: Project".

The project employs two OSEDA tools for physical design, which are accompanied with tutorials so as to guide the user in the first steps of the design. The first OSEDA tool is *Wgex* and is used for layout design with combined circuit extraction and Design Rule Checking (DRC) [19]. The second OSEDA tool is *Glade* and is used for generating and verifying schematics and layout with built-in DRC and Layout Versus Schematic (LVS) [20]. Figs. 1a and 1b show screenshots from these two tools.

The project is running for four years now and in total four fabrication runs have been performed using the FAIS technology. In each fabrication run, several circuits were designed by the members of the project, including analog, radio frequency (RF), and digital circuits, as well as sensors. Fig. 2 shows the microphotographs of two example circuits.

The project now also targets using the  $0.6\mu m$  technology provided by Phenitec Semiconductor Corp., Japan. Although

Fig. 2. Microphotograph of chips fabricated in the framework of the "MakeLSI: Project".

using this process requires a strict NDA for design rule disclosure, the project tried to avoid this by using directly the design rules of the FAIS  $2\mu m$  technology with a shrinking factor of  $\times 0.3$ . Some information has still to be provided by Phenitec Semiconductor Corp., such as contact and via size. MOSFET spice parameters were also fitted from measured fabricated devices, in order to generate the MOSFET simulation model and circumvent relying on the model included in the actual PDK. The MOSFET parameter extraction is performed by the OSEDA tool *PyEDA* [21].

In order to design the digital part of mixed-signal circuits, the project selected the *Alliance* OSEDA tool chain [10] and its included standard cell library. *Alliance* is a complete set of OSEDA tools based on symbolic unit  $\lambda$ , starting at RTL level and going all the way down to layout and GDSII. *Alliance* has a special layout tuning mechanism to migrate a symbolic layout into a real one. Therefore, the layout component dimensions generated with *Alliance* are not constrained to be multiple of  $\lambda$ , unlike other  $\lambda$ -based rule existing tools. This feature makes *Alliance* to be compatible with a wide range of technologies. The project has successfully fabricated LSI chips with *Alliance* using the 180nm ROHM technology [22] and the  $0.6\mu$ m Phenitec Semiconductor Corp. technology. Fig. 3 shows the design flow and a microphotograph of a fabricated chip [23], [24].

Fig. 3. NDA free design method and the generated chip layout

#### B. Electrical simulators

Ngspice [25] is one of the most popular mixed-signal circuit simulation tools. Its code is based on three open source software packages, namely Spice3f5 [26], Cider1b1 [27], and Xspice. It is an ongoing project that stared 15 years go, growing continuously with the help of new contributions suggestions, and reports from users.

#### C. Analog circuit sizing

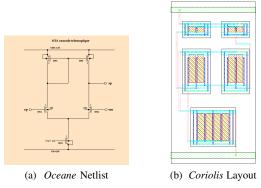

Oceane [28] is an OSEDA tool dedicated to the electrical sizing of analog circuits. Oceane provides a library of parametrized topologies of several analog functions, i.e. Operational Transconductance Amplifier (OTA), operational amplifier, comparator, voltage regulator, filters, switch, etc. The user has to select a technology, a topology, and set the values of the target performances. Oceane provides the sized topology in the form of a spice netlist [25], [26] and estimates of the performances, together with a set of benchmarks compliant with spice simulation so as to validate the estimated performances. The user can also perform statistical analysis to reach a centered design that will have a high fabrication yield.

#### D. Field-programmable analog array (FPAA)

FPAA is the analog equivalent of the field-programmable digital array (FPGA) and is perhaps the most popular OSHW platform for rapid and flexible AMS circuit design and prototyping [29], [30]. FPAA can enable configurable and programmable analog and digital computation and interfacing.

#### E. Benchmarks for analog test

Mentor Graphics and ams AG recently made available a set of benchmark AMS circuits with the aim to facilitate the development of fault models, design-for-test techniques, and test generation techniques, as well as their comparison based on fault coverage metrics and fault simulation times [31], [32]. The list of benchmark circuits includes an operational amplifier, a high-speed comparator, a power-on reset circuit, a charge-pump phase locked loop (PLL), and a 8-bit digital-to-analog converter (DAC). It is hoped that this set of benchmarks will boost the development of alternative, low-cost test techniques for AMS circuits, similarly to what happened for digital circuits following the publishing of digital benchmark circuits [33], [34].

#### F. SystemC AMS extensions

Virtual Prototyping (VP) is used for the design space exploration and verification of complex and heterogeneous embedded systems [35]. SystemC is a hardware description language for rapid VP of digital systems. In the framework of the European Project Catrene/BREAMS [36], the AMS extensions of SystemC [37] have been standardized by the Accellera consortium [38] under the OSCI [39] licence. In 2016, a new version of the Language Reference Manual [40] has been standardized by Accellera Systems Initiative [41] under the Apache licence [42], as well as by the IEEE consortium [43]. Version 2.1 of the simulator proof of concept has been recently released by COSEDA [44] compliant with the IEEE standard 1666.1 under the Apache 2.0 licence. SystemC AMS adds the Timed Data Flow (TDF) model of computation to SystemC, that handles analog signals sampled in time. The TDF model of computation is inspired by the Synchronous Data Flow model [45]. TDF models can interact with SystemC models thanks to converter ports. The SystemC AMS TDF model of computation is fully compliant with the discrete event simulator of SystemC [46], therefore mixed-signal system VP can be performed within the same simulation environment [47], [48].

#### G. Place & Route

Coriolis [49] is perhaps the only Place & Route EDA tool to be released as Free Open Source Software (FOSS) under the GPL licence [50]. The ongoing work of the Coriolis team is to extend its features to analog and mixed-signal circuits and systems [51]. It is now possible to take a netlist sized with Oceane and design the layout with Coriolis. Fig 4 shows the netlist of a simple OTA sized with Oceane and the corresponding layout designed with Coriolis.

Fig. 4. OTA sized with Oceane and its layout with Coriolis.

#### H. Layout viewer and editor

*KLayout* is a GDS and OASIS file viewer and editor [52]. It comes with a comprehensive documentation. It allows the drawing of any shape required by a technology process.

#### I. OSHW in health applications

echOpen [53] is an open and collaborative project and community, led by a multidisciplinary core of experts and senior professionals with the aim of designing a functional low-cost and open source echo-stethoscope (ultrasound probe) connected to a smartphone, allowing the radical transformation of diagnostic orientation in hospitals, general medicine and medically underserved areas.

#### V. Conclusion

We argued about the several benefits that OSEDA and OSHW can offer and pointed to the several difficulties that need to be overcome towards this goal. We also shed light on today's status of OSEDA and OSHW specifically for AMS circuit and system design and prototyping. While several OSEDA and OSHW exist and can be used to perform a low-cost design, it will require a larger collective effort to make OSEDA and OSHW trustful and useful in the context of practical and robust designs.

#### ACKNOWLEDGMENT

The authors would like to thank Jacky Porte for his work on the *Oceane* software and Luca Alloatti for the interesting discussions that inspired this paper.

#### REFERENCES

- R. M. Stallman, "Free hardware and free hardware designs." [Online].

Available: https://www.gnu.org/philosophy/po/free-hardware-designs.

ru-en.html

- [2] M. Ayass, "CERN Open Hardware Licence," 2017. [Online]. Available: https://www.ohwr.org/licenses

- [3] R. Stallman et al., "The gnu manifesto," 1985.

- [4] C. Anderson, Ed., Makers: The New Industrial Revolution. Crown Business, 2014.

- [5] S. Verhaegen, "The open source EDA tool chain for the Chips4Makers project. Is an ASIC made with fully open source tool chain possible? Is it affordable?" 2018. [Online]. Available: https://fosdem.org/2018/schedule/event/cad\_os\_asic/

- [6] J. Bonvoisin, "OPEN! Methods and tools for community-based product development," 2016. [Online]. Available: https://opensourcedesign.cc/wiki/index.php/OPEN!\_Methods\_and\_tools\_for\_community-based\_product\_development

- [7] University of California, Berkeley, EDA tools. [Online]. Available: https://embedded.eecs.berkeley.edu/pubs/downloads/

- [8] Arduino. [Online]. Available: https://www.arduino.cc/

- [9] A. Greiner and F. Pêcheux, "Alliance: A complete set of CAD tools for teaching VLSI design," in 3rd Workshop on VLSI design training, 1992, pp. 230–237.

- [10] "Alliance, A Free VLSI/CAD System," Université Pierre et Marie Curie-CNRS, LIP6. [Online]. Available: https://www-soc.lip6.fr/equipe-cian/ logiciels/alliance/

- [11] OpenCores project. [Online]. Available: https://opencores.org/

- [12] Open Hardware Repository. [Online]. Available: https://www.ohwr.org/

- [13] A. Katz, "Open Hardware License OHL v2.0," CERN. [Online]. Available: https://www.youtube.com/watch?v=RBnt\_9GadVM&index= 11&list=PLUg3wIOWD8ypZnjCc\_M08APZ7NSuET4G1

- [14] A. Barriga, "Visiting open source harware: A survey of opportunities," in *The 15th International Conference on Scientific Computing (CSC'17)*, 2017. [Online]. Available: https://csce.ucmss.com/cr/books/2017/LFS/ CSREA2017/CSC3193.pdf

- [15] Bonvoisin, J. et al., "What is the Source of Open Source Hardware?" Journal of Open Hardware, vol. 1, p. 5, 2017. [Online]. Available: http://doi.org/10.5334/joh.7

- [16] Software Heritage project. [Online]. Available: https://www.softwareheritage.org/

- [17] J. Akita, "Open Source LSI design & Fabrication Project for Distributed IP Development," in *International Conference on Analog VLSI Circuits* (AVIC), 2016.

- [18] "Semiconductor Center, Kitakyushu Science and Research Park," Kitakyushu Foundation for the Advancement of Industry, Science and Technology (FAIS). [Online]. Available: http://www.ksrp.or.jp/e/ shisetsu/semicon1.html

- [19] K. Asada, "Wgex." [Online]. Available: http://silicon.u-tokyo.ac.jp/en/research/

- [20] Peardrop Design Systems, "Glade." [Online]. Available: http://www.peardrop.co.uk

- [21] C. Drake, "Python library for electronic design automation." [Online]. Available: http://pyeda.readthedocs.io/en/latest/

- [22] T. Hosokawa and N. Shimizu, "The Layout Design Method for Rohm 0.18um Process Using Open Source EDA Tool-set and lambda rule based cell library Corresponding to Deep Sub-micron Process," Proceedings of the School of Information and Telecommunication Engineering Tokai University (Japanese), vol. 6, no. 1, pp. 23–30, 2013.

- [23] T. F. N. Shimizu, "Development of VLSI design Flow with FOSS EDA and NDA Free Design Rules," in *Proceedings of Asia Symposium on Engineering and Information(ASEAI)*, 2017, pp. 39–51.

- [24] N. Shimizu, "Development of NDA free VLSI design Flow for 0.6

Commercial Fabrication," in 12th International Conference on Innovative Computing Information and Control (ICICIC2017), 2017.

- [25] "nsgpice." [Online]. Available: http://ngspice.sourceforge.net

- [26] "The SPICE page." [Online]. Available: https://bwrcs.eecs.berkeley.edu/ Classes/IcBook/SPICE/

- [27] Berkeley. [Online]. Available: https://embedded.eecs.berkeley.edu/pubs/ downloads/cider/index.htm

- [28] J. Porte, "Oceane: Software tool for analog design and education." [On-line]. Available: https://www-soc.lip6.fr/en/team-cian/softwares/oceane/

- [29] A. Malcher and P. Falkowski, "Analog Reconfigurable Circuits," *International Journal of Electronics and Telecommunications*, vol. 60, no. 1, pp. 15–26, 2014.

- [30] S. George, S. Kim, S. Shah, J. Hasler, M. Collins, F. Adil, R. Wunderlich, S. Nease, and S. Ramakrishnani, "A Programmable and Configurable Mixed-Mode FPAA SoC," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 24, no. 6, pp. 2253–2261, 2016.

- [31] S. Sunter and P. Sarson, "A/MS benchmark circuits for comparing fault simulation, DFT, and test generation methods," in *Proc. IEEE International Test Conference*, 2017.

- [32] "Benchmarks for analog test," Mentor Graphics. [Online]. Available: https://www.mentor.com/products/silicon-yield/products/defectsim

- [33] F. Brglez, P. Pownall, and R. Hum, "Accelerated ATPG and fault grading via testability analysis," in *Proc. IEEE Int. Symposium on Circuits and Systems*, 1985, pp. 695–698.

- [34] F. Brglez, D. Bryan, and K. Kozminski, "Combinational profiles of sequential benchmark circuits," in *Proc. IEEE Int. Symposium on Circuits and Systems*, 1989, pp. 1929–1934.

- [35] J.-H. Oetjens et al., "Safety Evaluation of Automotive Electronics Using Virtual Prototypes: State of the Art and Reasearch Challenges," in Design Automation Conference, June 2014.

- [36] Serge Scotti et al., "Beyond Dreams: Design Refinement of Embedded Analogue and Mixed-Signal Systems," 2008-2011. [Online]. Available: http://projects.eas.iis.fraunhofer.de/beyonddreams/site/index/index en.html

- [37] Accellera Systems Initiative, "SystemC," 2017. [Online]. Available: "http://www.accellera.org/downloads/standards/systemc

- [38] M. Barnasconi et al., SystemC AMS extensions Users Guide, Version 1.0, Accellera systems initiative, March 2010. [Online]. Available: http://accellera.org/images/downloads/standards/ systemc/OSCI\_SystemC\_AMS\_extensions\_1v0\_Standard.zip

- [39] "SystemC Open Source Licence v3.3." [Online]. Available: http://accellera.org/images/about/policies/SystemC\_Open\_Source\_License\_v3.3.pdf

- [40] M. Barnasconi et al., SystemC AMS Extensions 2.0 Language Reference Manual, Accellera systems initiative, January 2016. [Online]. Available: http://accellera.org/images/downloads/standards/systemC\_AMS\_2\_0\_LRM-Apache.pdf

- [41] AMS Working group, "SystemC AMS Extensions," 2016. [Online]. Available: http://accellera.org/community/systemc/about-systemc-ams

- [42] the APACHE software foundation, "Apache licence." [Online]. Available: https://www.apache.org/licenses/LICENSE-2.0

- [43] IEEE, "IEEE Std 1666.1 standard," January 2016. [Online]. Available: https://standards.ieee.org/findstds/standard/1666.1-2016.html

- [44] K. Einwich, "SystemC AMS PoC2.1 Library, COSEDA, Dresden," 2016. [Online]. Available: http://www.coseda-tech.com/ systemc-ams-proof-of-concept

- [45] C. Ptolemaeus, Ed., System Design, Modeling, and Simulation using Ptolemy II. Ptolemy.org, 2014, http://ptolemy.org/books/Systems.

- [46] L. Andrade et al., "Pre-Simulation Formal Analysis of Synchronization Issues between Discrete Event and Timed Data Flow Models of Computation," in *Design Automation and Test in Europe (DATE)*, Grenoble, March 2015, pp. 1671–1677.

- [47] L. Andrade Porras, "Principles and implementation of a generic synchronization interface between SystemC AMS models of computation for the virtual prototyping of multi-disciplinary systems," Ph.D. dissertation, Université Pierre et Marie Curie, 2016.

- [48] C. Ben Aoun, "Principles and Realization of a Virtual Prototyping Environment for Composable Heterogeneous Systems," Ph.D. dissertation, Université Pierre et Marie Curie, 2017.

- [49] "Coriolis, Digital Place & Route," Université Pierre et Marie Curie-CNRS, LIP6. [Online]. Available: https://www-soc.lip6.fr/equipe-cian/ logiciels/coriolis/

- [50] GNU. [Online]. Available: https://www.gnu.org/licenses/gpl-3.0.en.html

- [51] E. Lao, M.-M. Louërat, and J.-P. Chaput, "Semi-automated analog placement based on margin tolerances," in *The 20th Workshop on Synthesis And System Integration of Mixed Information Technologies* (SASIMI 2016), Kyoto, Japan, 2016.

- [52] Koefferlein, Matthias, "KLayout," 2018. [Online]. Available: http://www.klayout.de/index.php

- [53] echOpen, "ECHOSTETHOSCOPY," 2018. [Online]. Available: http://www.echopen.org